解析英特尔Panther Lake技术亮点,深度评测酷睿Ultra 9 285H笔记本性能表现。

【ZOL原创技术解析】此前,我们已对英特尔PantherLake处理器的架构和核心IP设计进行了较为全面的分析,了解了其在能效与性能方面的表现,以及CPU、GPU、NPU、IPU等计算单元的新特性与升级点。然而,在一些技术细节方面,如封装方式、分支预测机制、线程调度策略、电源管理方案,以及GPU/NPU计算单元的具体技术实现等方面尚未深入探讨,因此有了这篇关于PantherLake的“技术细节补完”内容。

作为Intel 18A制程工艺打造的首款移动端处理器平台,PantherLake在延续上一代LunarLake高能效优势的同时,也吸收了ArrowLake的高性能特点。相比前代产品,其在CPU和GPU性能方面均提升了50%,这一幅度的提升在近年来的移动端处理器发展中较为少见。令人印象深刻的是,在性能显著增强的前提下,PantherLake依然维持了优秀的能效表现,充分展现了Intel 18A制程的技术实力。 从市场角度来看,这种性能与能效的双重突破,不仅体现了Intel在移动端持续发力的决心,也为未来笔记本电脑和其他移动设备的性能提升提供了新的可能性。在竞争日益激烈的处理器市场中,这样的进步无疑为消费者带来了更多选择与期待。

・Intel 18A制程工艺的核心优势来自于两大关键技术突破

那么,肯定有朋友会提出疑问——Intel 18A制程工艺的核心优势究竟在哪里?

其实答案的关键在于两大核心技术的突破:RibbonFET全环绕栅极晶体管技术以及PowerVia背面供电技术。这些技术的出现,标志着半导体行业在提升性能和能效方面迈出了重要一步。RibbonFET通过更高效的电流控制,为未来芯片设计提供了更强的灵活性,而PowerVia则通过优化电源传输路径,进一步提升了芯片的整体表现。这两项技术的结合,不仅推动了制程工艺的进步,也为下一代高性能计算设备奠定了基础。

了解半导体芯片的人应该都清楚,性能的提升本质上来自于晶体管密度的持续增加。然而,对于芯片制造商而言,在提高晶体管密度的同时,还要不断缩小芯片的尺寸,这在高制程节点下带来了良率、供电稳定性、漏电以及散热等方面的巨大挑战。

Intel 18A制程工艺之所以能在1.8nm节点上通过提升晶体管密度来增强性能,同时保持出色的能效表现,关键在于确保良率的前提下,采用了RibbonFET全环绕栅极晶体管技术以及PowerVia背面供电技术,有效解决了供电、漏电和发热等关键技术难题。

另外在10月初笔者受英特尔邀请前往美国亚利桑那州凤凰城参观英特尔Fab52晶圆厂时,已经看到有ASML光刻机正在量产Panther Lake芯片,这意味着其良率已经达到了正式投产的要求。而且Intel 18A现阶段的良率其实已经高于英特尔在过去十五年推出的制程节点。

RibbonFET全环绕栅极晶体管采用了全环绕栅极(GAA)结构,通过垂直堆叠的带状沟道设计,提升了晶体管的密度与能效,并实现了对电流的精确控制。在实现晶体管进一步缩小的同时,有效减少了漏电现象。从下图可以看出,传统FinFET晶体管每个鳍片仅实现三面通电,而RibbonFET全环绕栅极晶体管每个鳍片均可实现四面全包围通电,不仅显著降低了漏电率,还大幅缩小了整个晶体管的体积。

晶体管作为半导体芯片中最核心的元件,直接决定了芯片的性能表现。在实际使用中,积热导致的处理器频率下降是影响用户体验最明显的问题之一。同时,芯片性能的提升与晶体管密度密切相关,随着芯片面积不断缩小,而晶体管数量却持续增加,这种看似矛盾的发展趋势对技术提出了更高要求。为此,RibbonFET全环绕栅极晶体管等创新技术应运而生,成为突破当前瓶颈的关键手段,有助于在更高晶体管密度下维持稳定的性能输出,避免因电流和温度问题而受限。 从行业发展趋势来看,技术创新始终是推动半导体产业前进的核心动力。RibbonFET等新型晶体管结构的出现,不仅体现了技术上的进步,也为未来更高效、更节能的芯片设计提供了可能。这一突破对于提升整体计算能力、优化能效比具有重要意义,也预示着半导体行业正朝着更精细化、更智能化的方向迈进。

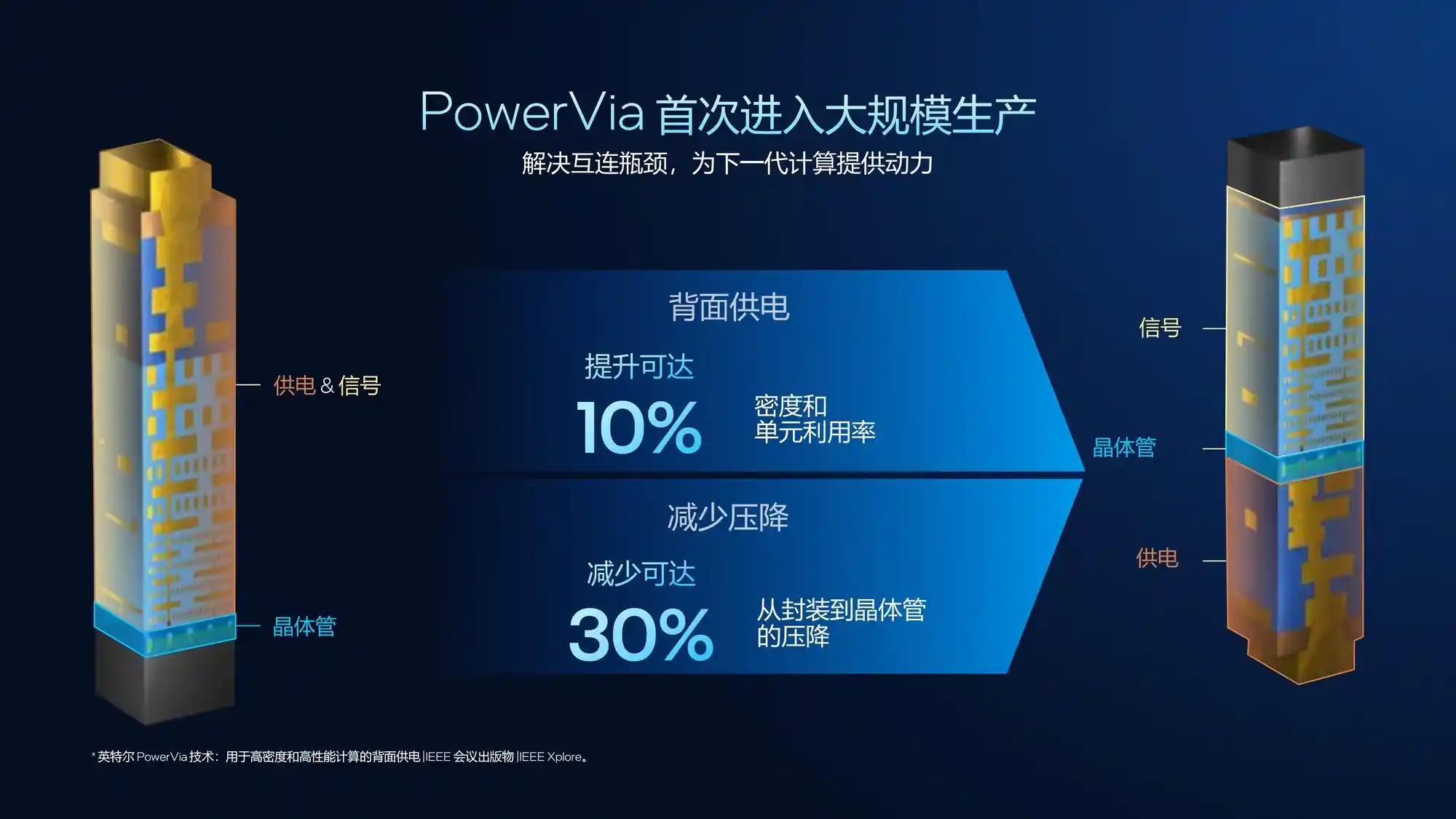

PowerVia背面供电技术对芯片制造工艺进行了全面升级,随着越来越多的应用场景需要更小尺寸、更高密度和更强性能的晶体管来应对持续增长的算力需求,传统的混合信号线与电源布线一直占据着晶圆内的同一空间,造成布局拥堵,进一步增加了晶体管微型化的难度。这一技术的引入,为解决空间资源紧张提供了新的思路,有助于推动芯片性能的持续提升。

PowerVia背面供电技术通过将粗间距金属层和凸块移至芯片背面,并在每个标准单元中嵌入纳米级硅通孔(nano-TSV),有效提升了供电效率。该技术在ISO功耗效能方面最高可提升4%,同时使标准单元利用率提高5%至10%。这一创新不仅优化了芯片的能源管理,也为高性能计算和低功耗设计提供了新的可能性。 从行业角度来看,PowerVia的推出标志着芯片设计在供电架构上的重要突破。将关键结构移至背面,不仅有助于减少正面布线的复杂性,还能提升整体性能与能效。随着半导体工艺不断向更小节点演进,这种技术的推广或将推动整个行业向更高效、更紧凑的方向发展。

得益于两项关键技术的突破,首款采用Intel18A制程的处理器PantherLake在芯片性能、密度和能效方面实现了显著提升。 从行业发展趋势来看,制程工艺的每一次进步都意味着计算能力的跃升与能耗的优化。此次Intel18A制程的推出,不仅标志着英特尔在先进制程上的持续突破,也为其在竞争激烈的半导体市场中增强了技术话语权。PantherLake作为这一技术的首发产品,无疑将为未来高性能计算、人工智能以及边缘计算等领域带来更强大的支持。

・封装

制程技术的突破为PantherLake奠定了坚实的基础,但要真正释放这些技术的优势,先进封装技术的支持同样不可或缺。2023年9月,笔者应英特尔邀请,参观了其位于马来西亚槟城的PG8、PG15、PG16三个封装厂区,以及位于居林(Kulim)的DSDP/SIMS工厂,深入了解了英特尔在2D和3D封装技术方面的强大实力。 从此次访问中可以看出,英特尔在封装领域的布局已相当成熟,不仅拥有先进的工艺能力,还具备大规模量产的稳定性和可靠性。这表明,英特尔正通过整合制程与封装技术,构建更完整的芯片制造生态,以应对日益复杂的市场和技术挑战。未来,随着3D封装等技术的进一步发展,英特尔在高性能计算领域的竞争力有望持续增强。

此次发布的PantherLake堪称英特尔在先进封装技术领域的又一杰出成果。

首先,英特尔通过EMIB-M 2.5D技术,帮助自家新一代处理器实现了关键性能突破:一方面缩小了Bump pitch(凸块)的间距,并且提升了Bump density,也就是密度,另一方面还显著的降低了芯片间C2C的功耗含量,增强了信号的完整性和效率。

同时,英特尔通过Foveros Direct 3D封装技术(Panther Lake使用到的是Foveros-S 3D封装),将以往的凸块直连改变为铜对铜的混合键合,其好处是带来了更高的密度、更低的延迟、更低功耗的互连,这也是未来大规模系统级集成的核心技术。另外尤其是用在服务器方面,它可以为更大面积的芯片,更大规模的互连带来极大好处,比如与Panther Lake一同推出的288核小核的Clearwater Forest,也就是至强6+处理器上,这项封装技术实现了量产。

Panther Lake主要使用了Foveros-S 2.5D封装技术,各个功能模块和被动基础模块相连,充分发挥其在高密度、高能耗场景下的优势。

此前我们在Panther Lake技术解析文章中介绍了它的全新性能核以及能效核架构,本文不再赘述。下面我们从性能核和能效核的相关技术优化,来聊聊Panther Lake的性能为何会有50%的提升幅度。

・性能核优化

首先我们来看看性能核的相关技术优化。

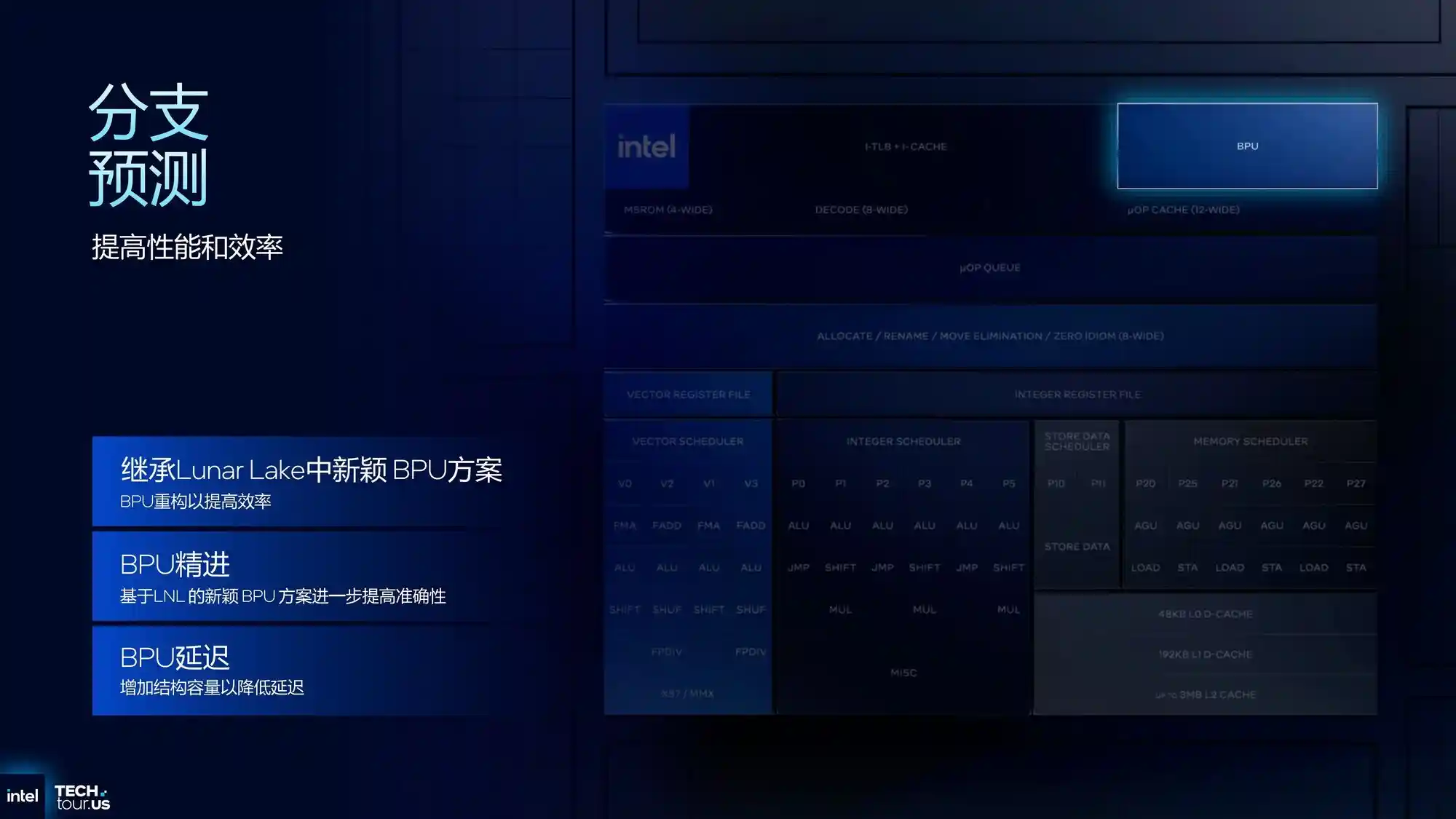

分支预测

除了核心架构之外,分支预测也是现代处理器提升性能的关键技术之一。出色的分支预测能够减少流水线的停滞,优化指令的提前加载与缓存命中,应对复杂的控制流,并且有助于编译器和代码的优化。

Panther Lake的分支预测并非推到重来,而是在前代Lunar Lake引入分支预测新算法的基础上,进行了深度迭代与优化,目的是让分支预测效率更高。同时Panther Lake的分支预测准确度也得到了进一步提升。

了解处理器技术的读者都知道,分支预测的关键在于CPU提前判断程序执行路径中可能遇到的分支,并做好相应准备。这包括对分支方向的预测,以及预测结果反馈到CPU核心流水线的速度。在PantherLake这一代架构中,相比LunarLake,分支预测在准确性上有了进一步提升,同时预测延迟也大幅降低。这意味着CPU在预测和修正上的开销减少,从而将更多时间用于实际的计算任务,显著提高了有效计算时间的比例。最终,用户的直观感受就是CPU性能有了明显提升。

内存消歧

除了分支预测之外,针对内存密集型任务,PantherLake的内存别名消除技术在提升性能体验方面也起到了显著的作用。

从传统角度来看,CPU在处理内存读写操作时,通常需要严格按照指令顺序执行。例如,某个读取操作可能依赖于之前写入操作的结果,或者多个操作指向同一内存地址时,也必须按顺序进行。这种严格的依赖关系使得内存单元常常处于等待状态,导致内存带宽的利用率不高,难以充分发挥硬件的性能潜力。

内存消歧技术的关键在于,它能够智能地预测并消除这种表象上的依赖关系,使CPU的多个执行单元可以进行乱序或并行的内存读写操作,从而更高效地利用内存带宽。

当然,在实际编程中,内存依赖关系仍然不可避免。内存消歧技术的精妙之处在于,它能够准确判断哪些操作可以安全地并行执行,哪些存在真实的依赖关系。如果预测出现偏差或检测到实际冲突,该技术能够在极短时间内进行恢复,从而保障程序运行的正确性。 我认为,这种技术的发展对于提升系统性能和稳定性具有重要意义。随着多核处理器和并行计算的普及,如何高效管理内存访问成为关键挑战。内存消歧技术的进步不仅有助于优化程序执行效率,也为开发者提供了更可靠的底层支持,推动了高性能计算领域的持续发展。

通过这一机制,可以显著提高CPU与内存之间的带宽利用率。在CougarCove平台上,这种内存消歧技术相比前代产品LionCove有了明显改进,其消歧性能更加稳定,细节处理更精准,并且恢复速度更快。

TLB增强

此外,英特尔对Panther Lake进行TLB升级。TLB简单理解就是一种缓存,其本质上是CPU内部虚拟地址到物理地址的映射缓存。对于混合型工作负载,TLB至关重要。它避免了CPU频繁访问系统内存进行耗时的页表遍历,而是将常用的地址映射预先存储,实现快速查找。这极大地加速了内存访问,显著提升了复杂场景下的性能。

这一次在Panther Lake平台上,英特尔通过采用Intel18A先进制程以及PowerVia等关键技术,实现了TLB容量提升1.5倍,将TLB容量扩大了50%,从而为现代复杂的工作负载带来了更佳的性能体验。

另外,Panther Lake性能核其实还能够做到16.67MHz的精准时钟频率间隔,这意味着内部能够实现更精细的性能与能效调控,从而提供更快速的响应和更精确的核心性能与功耗管理。

・能效核优化

与性能核类似,能效核在分支预测能力和内存冲突消除方面也进行了相应优化,此处不再重复说明。

动态预取器控制

首先我们来聊聊动态预取器控制。

预取器的主要功能是预测CPU接下来需要的数据和指令,并提前将它们从内存加载到缓存中,从而确保执行单元能够持续高效运行,减少因等待数据而造成的空闲时间。动态特性体现在,PantherLake的预取器可以根据当前的工作负载类型以及实时变化的情况,智能地调整预取策略。这不仅有助于最大程度保持执行单元的活跃状态,提升整体性能,还能在某些情况下通过优化预取行为,有效降低不必要的能耗。

Nanocode

Nanocode可以理解为比传统Microcode更底层的微操作指令。Microcode通常面向CPU的逻辑模块,定义了如何执行一条复杂指令。而Nanocode则将Microcode进一步分解,直接面向前端的硬件执行小单元,例如一个独立的加法器或加载单元。这种更细粒度的控制,使得Panther Lake能够更精准、更灵活地调度硬件资源。

举例来说,当某个执行单元由于微码的粗粒度设计而无法得到充分利用时,纳米码技术能够突破这一限制,将任务中的细小部分分配给当前空闲的硬件单元。通过这种方式,PantherLake显著提升了硬件资源的使用效率,从而大幅增强了整体性能,并减少了CPU的执行延迟。

相较于前代ArrowLake平台,PantherLake的Nanocode能够适配的应用场景更加广泛。过去可能仅针对几种特定类型的负载进行优化,而在PantherLake中,其适用范围进一步扩展,这意味着在更多不同的使用场景下,PantherLake可以更充分地发挥能效核的性能优势和低功耗特性。

GPU部分

作为移动端平台的一部分,PantherLake的iGPU同样备受关注。毕竟LunarLake的锐炫140V/130V核显在图形性能上的表现令人印象深刻,甚至让轻薄本和商务本具备了在1080p分辨率、中低画质下运行3A游戏的能力,这一突破彻底改变了轻薄本和商务本的应用场景。 从行业发展趋势来看,核显性能的持续提升正在逐步模糊传统笔记本的定位界限。以往高性能图形处理往往依赖独立显卡,而如今,凭借不断增强的集成显卡,轻薄本也能承担起更多元化的使用需求。这种变化不仅提升了用户体验,也为厂商在产品设计上提供了更大的灵活性。随着技术的进一步发展,未来我们或许能看到更多搭载高性能核显的轻薄设备出现在市场中。

PantherLake的GPU搭载了全新的Xe3架构,新增支持多帧生成技术,同时核心规模也实现了显著扩展。因此,预计明年PantherLake产品发布后,其图形性能将带来令人惊喜的提升。

下面咱们看看为什么我们会如此期待Panther Lake的iGPU的表现。

这次Panther Lake的iGPU优化主要是扩展性层面的提升,这使其核心实现了更大的规模。单个渲染切片最多包含的Xe核心达到了6个,顶配型号拥有12个Xe核心,这种核心规模的升级对于GPU而言就是最直接的性能提升手段。

同时,PantherLake将GPU模块独立于计算模块之外,因此在核心规模的配置上相比以往更加灵活。首批产品提供4核和12核两种版本,随着后续型号的不断丰富,Xe核心的数量将会更加灵活多变。这与以往将GPU集成在计算模块中、无法进行调整的设计方式不同。

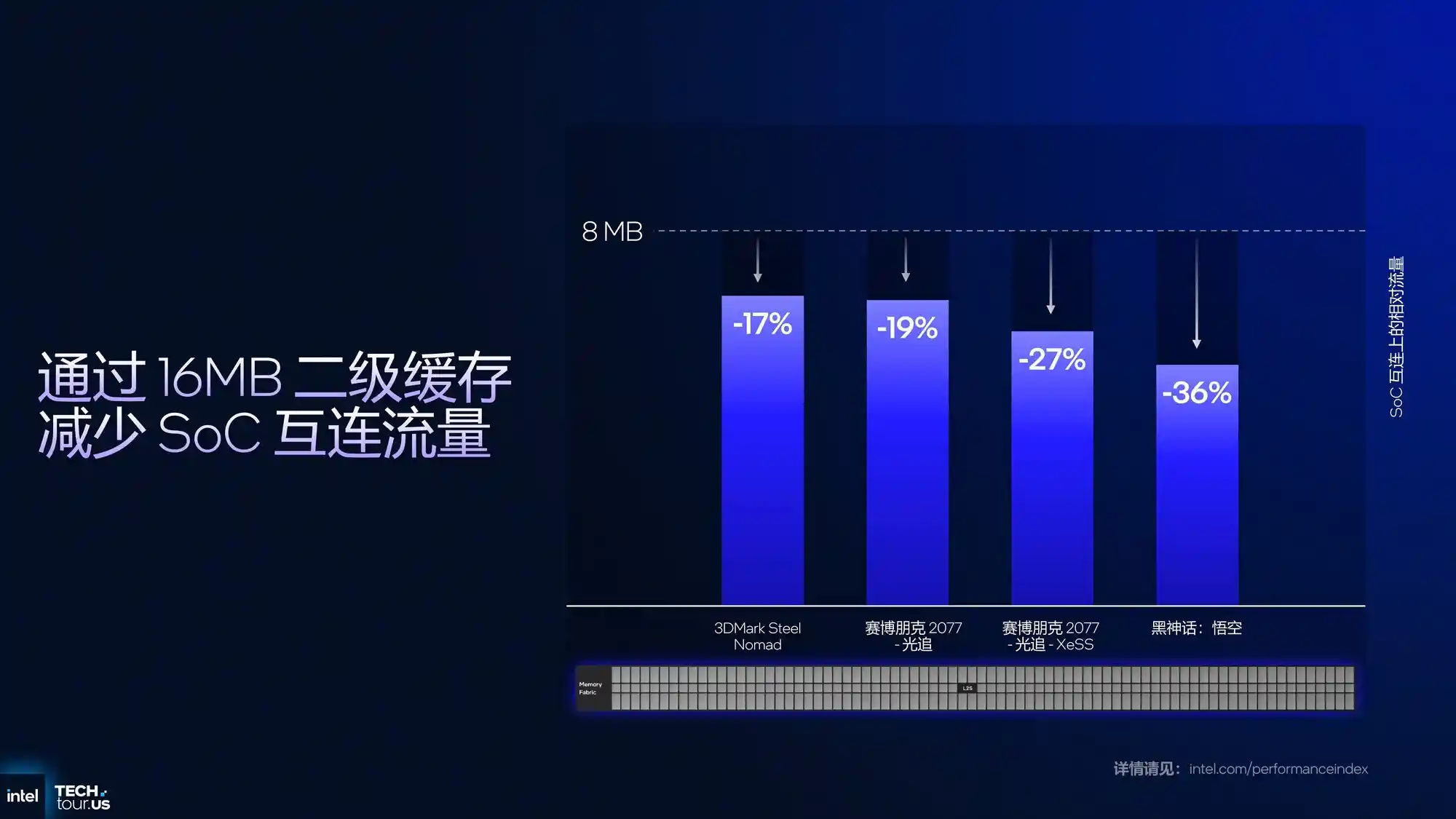

同时,12核心GPU还提供了更大的二级缓存容量,由此前的8MB提升到16MB,更大的L2缓存可以减少约17%到36%的对主内存的访问次数,通过更低频次的内存访问,提供更流畅的体验。

核心规模拓展加上L2缓存扩容之外,关键计算单元的性能优化也是Panther Lake iGPU体验提升的关键一环。这里包含了第三代Xe核心、更强的光追单元、更好的矢量引擎以及更出色的图形专用硬件管线。

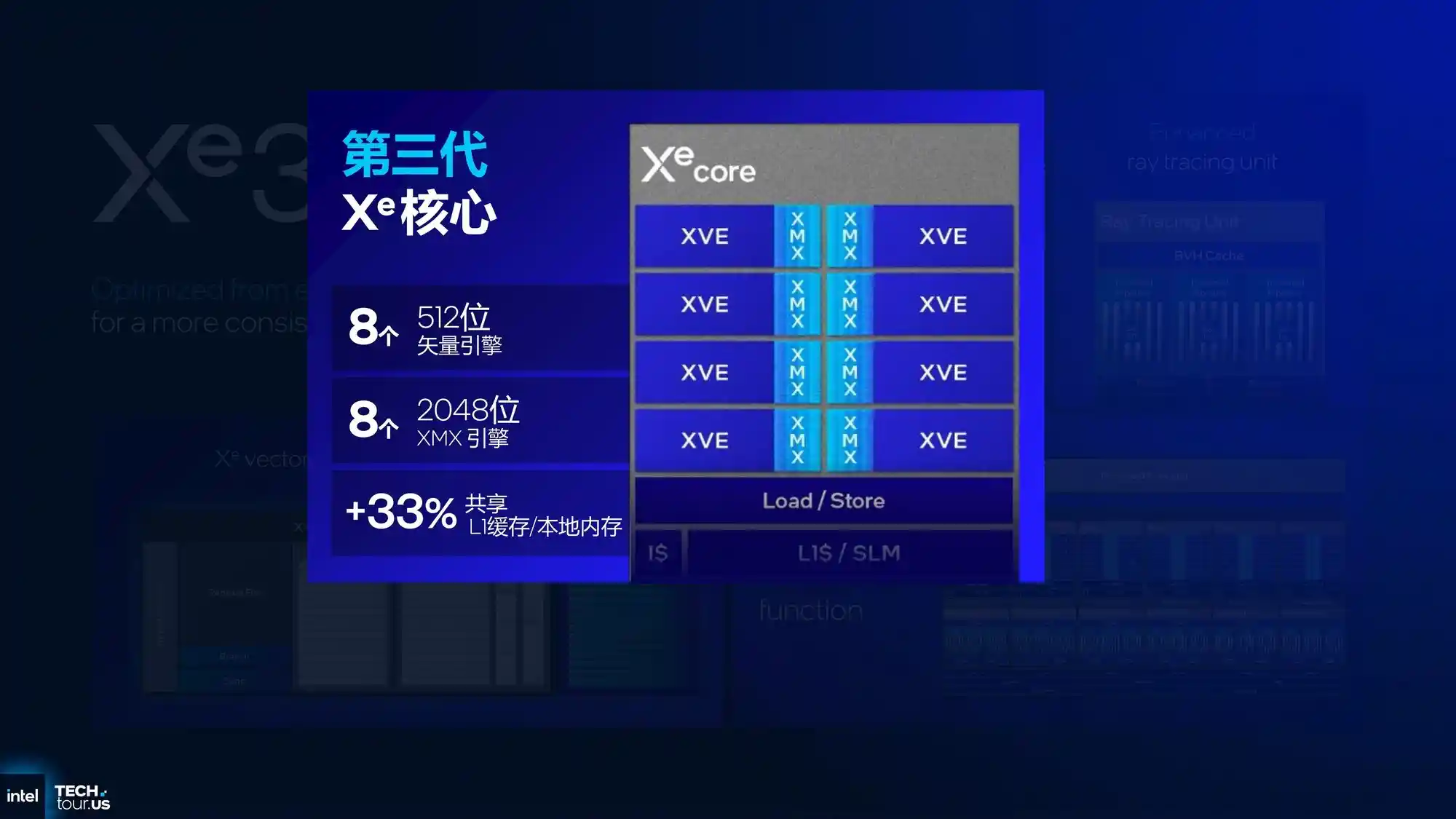

在Xe3核心中,提供了8个512位矢量引擎和8个2048位XMX引擎,并且将L1缓存增加了三分之一,赋予了Xe核心更强大的性能。

在Xe矢量引擎中,线程数量提升了25%,同时引入了可变寄存器分配机制。通过增加线程数和采用可变寄存器分配,英特尔显著提高了Xe矢量引擎的使用效率,使相同硬件能够处理更多、更快速的任务。此外,PantherLake的iGPU支持原生FP8反量化功能,以及SIMD16原生ALU、三路并发、扩展数据指令集和FP64运算,并且支持Xe矩阵扩展。

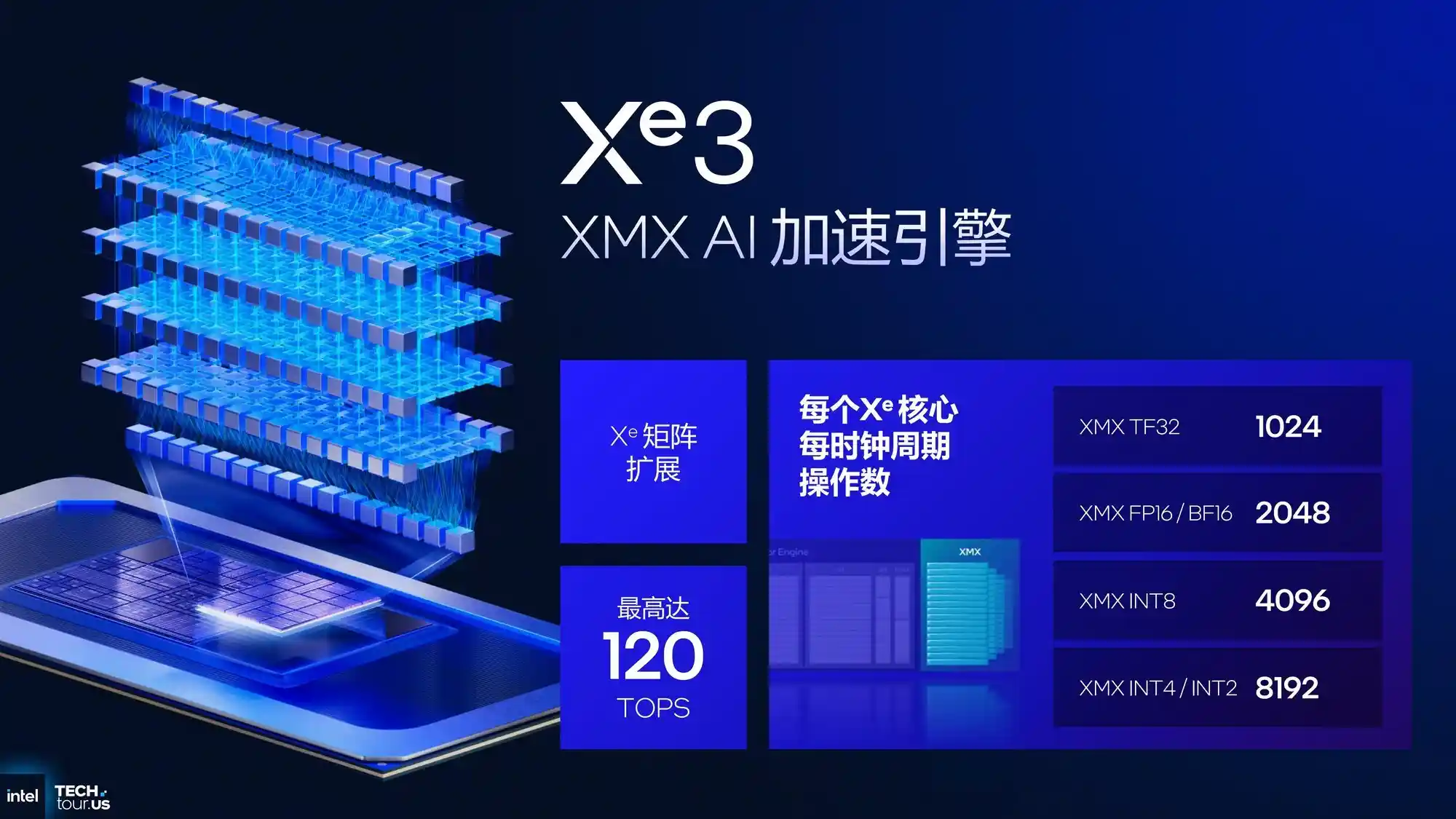

此外,这一代iGPU在AI算力方面提升至120TOPS,实现大幅跃升的关键在于XMXAI加速引擎。该引擎每个时钟周期可执行1024个XMXTF32操作,支持2048个XMXFP16/BF16运算,4096个XMXINT8运算以及8192个XMXINT4/INT2运算,各项指标均较上一代有明显提升。

从这一代产品开始,光追单元支持异步光线追踪的动态光线管理。实际上,在光线追踪技术中,最困难的部分之一就是处理海量光线。当光线数量过多,超出硬件处理能力时,就会出现拥塞现象。此时,GPU需要一种更高效的调度机制,在拥塞发生前降低光线的分发频率,这自然对调度器的设计提出了更高要求。Xe3支持新一代的异步光线追踪动态光线管理,能够在光线追踪负载下显著提升性能。

GPU性能提升的另一项重要优化在于固定功能管线的改进。其中核心亮点是英特尔为PantherLake的GPU引入了全新的URB管理器,进一步提升了图形处理效率。 在我看来,URB(Unified Return Buffer)管理器的升级表明英特尔在GPU架构设计上正逐步走向精细化和高效化。这种改进不仅有助于提升整体图形性能,也为未来更复杂的应用场景打下了基础。随着URB管理机制的优化,系统资源的调度将更加合理,从而带来更流畅的用户体验。

URB作为GPU内部用于子单元间数据转换与传输的存储单元,传统设计中即便仅需传输少量数据,也需对整个URB进行同步操作,导致效率较低。新推出的URB管理器支持对部分URB进行传输同步,最高可实现2倍的异向性过滤能力,从而将模板测试速率提升至原来的2倍。 这种改进在提升性能的同时,也反映出GPU架构在细节优化上的持续进步。通过更精细的资源管理,不仅提高了数据传输效率,也为复杂计算任务提供了更高效的底层支持。这样的技术演进对于图形处理、并行计算等领域具有重要意义。

基于上述升级,Panther Lake的Xe3核显性能非常让人期待。

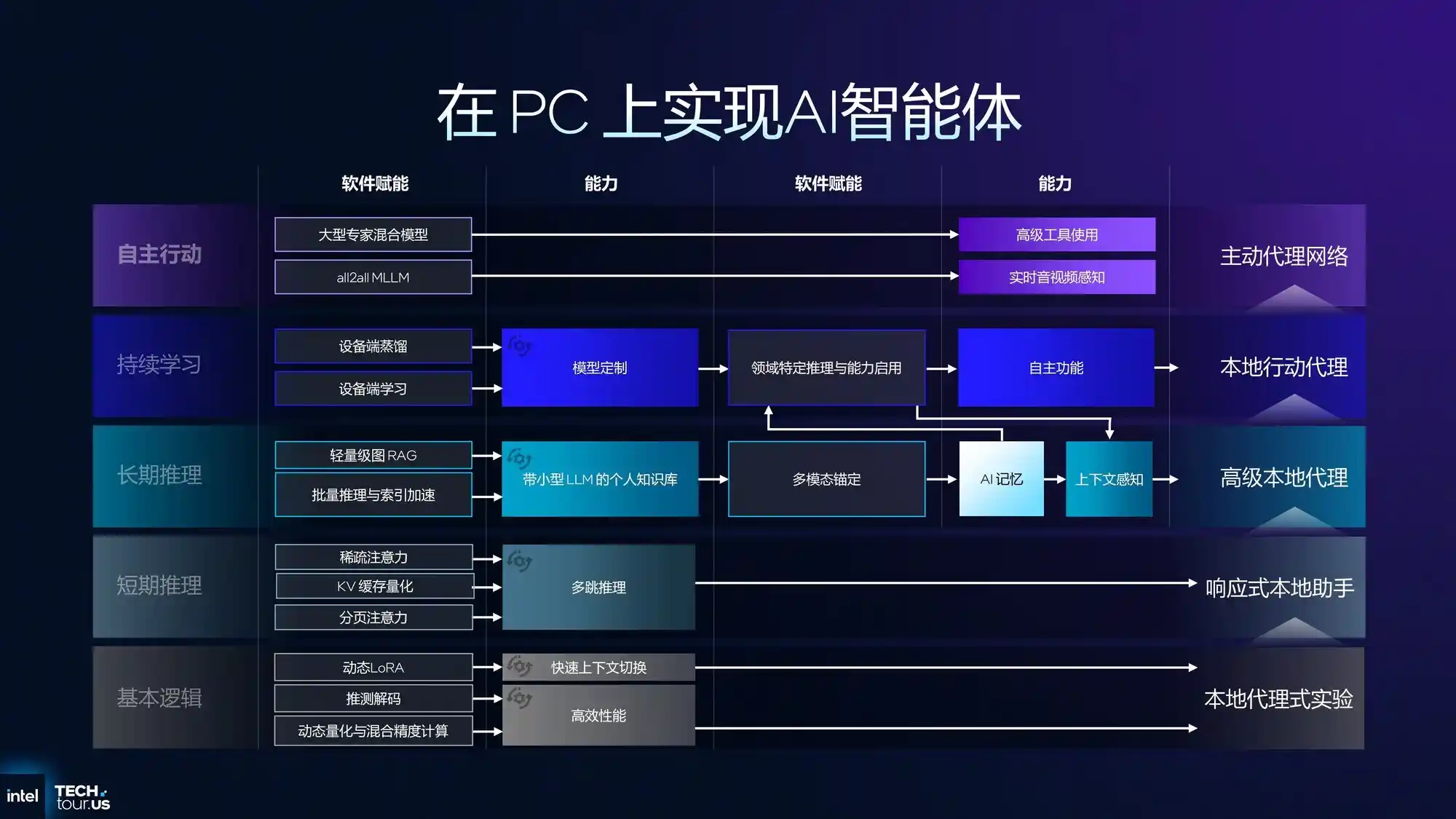

随着CPU与GPU性能的持续提升,PantherLake在NPU、IPU、内存性能以及无线连接能力等方面也实现了显著升级。依托这些技术进步,英特尔正积极推动PC行业合作伙伴开发支持高效AI智能体的新型PC产品。通过强大的硬件配置和完善的软件生态,构建本地化的AI智能体,使电脑更加智能化。用户只需输入一两条指令,系统便可自动调用各类软件完成复杂的工作流程,这种理念无疑代表了未来PC发展的重要方向,具有较强的前瞻性和创新性。

总体来说,作为Intel 18A制程工艺的首个处理器平台,PantherLake的表现备受关注。据官方透露,预计在明年1月于拉斯维加斯举行的CES展会上,将首次展出搭载PantherLake的新产品。笔者近期已收到多家PC厂商的CES参展邀请,若行程顺利,届时将从展会现场带来第一手的PantherLake新品报道。